According to "

PCI Interrupt Handling on DM6467/DM6467T PCI Host", DM6467/DM6467T devices do not have PCI interrupts input lines (INTA, INTB, INTC, INTD). Thus the default EVMs cannot receive PCI interrupts from targets connected over the bus and in turn, cannot interrupt DM6467 ARM on the same. This can be worked around by using GPIO lines to receive PCI interrupts from the PCI slot to which DM6467 PCI Host EVM is connected. This requires using wires to get the INTA...D lines from the slot and connect them to DM6467 GPIO lines and modify the Host Controller driver accordingly.

Hardware Modifications

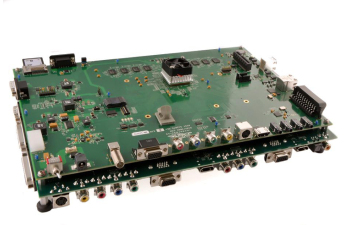

Use wires to connect PCI interrupt lines from target device(s) from respective slots to DM6467 PCI Host's GPIO pins. Following figures show 2 of the possible arrangements when using 4 target devices:

Software Modifications

/* Setup DM6467 for PCI mode. In case of default EVM, the CPLD along with FET

* switches takes care of switching to PCI Boot mode when the EVM is put in

* the PCI slot and this funtion needs to do nothing. While in case when the

* CPLD code/ Hardware is reworked (not to do autoswitch), the code below

* handles mux configurations to switch to PCI (Host) mode and takes care of

* driving RST# over PCI Bus.

*

* Note: This function relies on h/w setting of PCIEN to distinguish between

* modified and unmodified EVM and might not work in case s/w (e.g., bootloader)

* is manipulating PCIEN after booting.

*/

static void dm646xevm_pci_setup(void)

{

void __iomem *base = IO_ADDRESS(DAVINCI_SYSTEM_MODULE_BASE);

/* Skip this if PCIEN is already set in PINMUX0 */

if (!((__raw_readl(base + PINMUX0)) & (1<<2))) {

/* Power up the I/O cells for PCI interface */

__raw_writel(__raw_readl(base + DM64XX_VDD3P3V_PWDN)

& ~(3<<16), base + DM64XX_VDD3P3V_PWDN);

davinci_cfg_reg(DM646X_HPI32EN);

/* Drive GPIO[13] High to avoid reset when PCI is

* enabled

*/

if (gpio_request(13, "RST#") != 0) {

pr_err("Request for GPIO13 failed.\n");

return;

}

gpio_direction_output(13, 1);

/* Ensure AUDCK1 is disabled to control GPIO[2] */

davinci_cfg_reg(DM646X_AUDCK1);

davinci_cfg_reg(DM646X_PCIEN);

/* Drive GPIO[2] high to take the PCI bus out of reset

* (drive RST#) and select B2 of the FET mux on EVM to

* deselect NAND and switch to PCI Bus

*/

if (gpio_request(2, "PCIRST#") != 0) {

pr_err("Request for GPIO2 failed.\n");

return;

}

gpio_direction_output(2, 1);

} else {

pr_info("PCI_EN is already asserted.\n");

}

}

static void board_init(void)

{

#define REG_PINMUX0 __REG(0x01C40000)

#define REG_GPIO_DIR01 __REG(0x01C67010)

#define REG_GPIO_OUT_DATA01 __REG(0x01C67014)

/* Setup PSCs for Required Components */

board_setup_psc(DAVINCI_GPSC_ARMDOMAIN, DAVINCI_DM646X_LPSC_GPIO, 1);

board_setup_psc(DAVINCI_GPSC_ARMDOMAIN, DAVINCI_DM646X_LPSC_PCI, 1);

...

/* Set Mux Mode to GPIO */

REG_PINMUX0 = 0x2;

/* Set Direction of GPIOs to ‘OUT’ */

REG_GPIO_DIR01 = 0x0;

/* Drive GPIO[13] High */

REG_GPIO_OUT_DATA01 = 0x2000;

/* Set Mux Mode to PCI */

REG_PINMUX0 = 0x4;

/* Drive GPIO[2] High */

REG_GPIO_OUT_DATA01 = 0x2004;

}

DM6467 PINMUX Registers PINMUX0 and PINMUX1 in the System Module are responsible for controlling all pin multiplexing functions on the DM6467. The following peripherals have multiplexed pins: VPIF, TSIF0, TSIF1, CRGEN0, CRGEN1, EMIFA, PCI, HPI, ATA, PWM0, PWM1, UART0, UART1, UART2, Audio Clock Selector, the USB USB_DRVVBUS pin, and GPIO.

The Pin Multiplexing 0 Register controls the pin function in the EMIFA, ATA, HPI, PCI, TSIF0, TSIF1, and CRGEN. Some muxed pins are controlled by more than one PINMUX bit field. The Pin Multiplexing 1 Register controls the pin function in the UART0, UART1, and UART2 Blocks.

This utility allows the pin multiplexing registers

of the device to be calculated with ease, as well as showing what peripherals

can be used together.