Video Timing Detail

Tomi Engdahl gave a very good description of video timing detail and calculator.

In the above picture,

- Green dots are the visual side of sceen.

- Black dots are the black border or the screen and the pixels where the cathode ray is outside the picture.

- White dots are the sync pulses. The beginning of these pulses position the picture on the screen.

- A is the amount of dots or display pixel, for example, 1080 in a 1080p monitor.

- B is the start place of horizontal sync-pulse. If will remain in constant phase, so if you increase it the picture will move to left and if you decrease it the picture will mode to right.

- C is the end of the sync pulse. It contains no relevant information, just put something between B and C that is something like b+20 or b+100, it won't really make much difference.

- D if the end of the line. It affects to 2 things. First the ratio a/d affects the wideness of the visual picture. Secondly Horizontal frequency "J" (khz) is counted from the following formula:

1000*I 1

J= -------- time= ----------

D frequency

This means that if you decrease dot clock "I" then the horisontal frequncy will decrease and vise versa. If you increase the line length "D" then the horisontal frequency will decrease and vise versa.

E, F, G, and H are the corresponding vertical definitions.

Modeline in Depth

A modeline is a configuration line in xorg.conf or the XFree86 configuration file (XF86Config) that provides information to the X server about a connected computer monitor or television and how to drive it at a specified display resolution. The Modeline is based on the Generalized Timing Formula or the Coordinated Video Timings standards produced by VESA. Modelines are now all but unused, but XFree86 and the Xorg Server still allow them to be set should the EDID information be inadequate.

A modeline for a 1080p60:

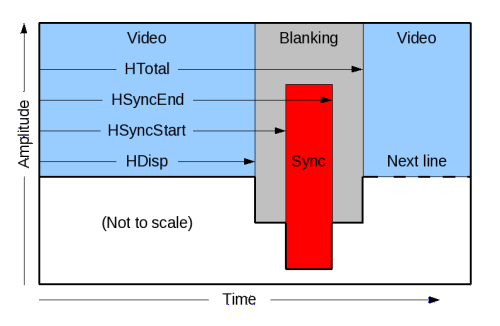

Modeline: "1920x1080" 148.500 1920 2008 2052 2200 1080 1084 1089 1125 +hsync +vsync

Here's a modeline with descriptive labels instead of numbers:

Modeline: "String description" Dot-Clock HDisp HSyncStart HSyncEnd HTotal VDisp VSyncStart VSyncEnd VTotal [options]

Here is a diagram that shows how some of the labels correspond to a horizontal line of video:

The "Dot-Clock" or "Pixel Clock", with units of megahertz, is the rate at which pixels are drawn. In this example with a dot-clock of 148.5*10E6 Hz, a pixel is drawn every 1/(148.5*10E6 Hz) or roughly every 7 nanoseconds. Computing the dot-clock is actually one of the simpler parts of the modeline computation — it's equal to the refresh rate * HTotal * VTotal (the '*' asterisk is used in computer programming to signify multiplication):

Refresh rate * HTotal * VTotal = Dot Clock (Pixel Clock)

60*2200 * 1125 = 148,500,000 or 148.5 * 10E6 Hz

EDID

EDID (Extended display identification data) is a data structure provided by a digital display to describe its capabilities to a video source (e.g. graphics card or set-top box). It is what enables a modern personal computer to know what kinds of monitors are connected to it. EDID is defined by a standard published by the Video Electronics Standards Association (VESA). The EDID includes manufacturer name and serial number, product type, phosphor or filter type, timings supported by the display, display size, luminance data and (for digital displays only) pixel mapping data.The VESA E-EDID Standard requires that the first detailed timing descriptor be the “preferred” video format and subsequent detailed timing descriptors listed in order of decreasing preference. A EDID Detailed timing descriptors example for 1080p60 is

Detailed Descriptor #1: Preferred Detailed Timing (1920x1080 @ 60Hz)

Pixel Clock : 148.5 MHz

Horizontal Image Size : 160 mm

Vertical Image Size : 90 mm

Refresh Mode : Non-interlaced

Normal Display, No Stereo

Horizontal:

Active Pixels : 1920 Pixels

Blanking Pixels : 280 Pixels

Sync Offset : 88 Pixels

Sync Pulse Width: 44 Pixels

Border : 0 Pixels

Vertical:

Active Pixels : 1080 Lines

Blanking Pixels : 45 Lines

Sync Offset : 4 Lines

Sync Pulse Width: 5 Lines

Border : 0 Lines

Pixel Clock = dot clock

Active Pixels = HDisp

Blanking Pixels = HTotal - HDisp

Sync Offset =

HSyncStart - HDisp

Sync Pulse Width = HSyncEnd - HSyncStart

The DM646x video port interface (VPIF) is an example of VPIF which is a receiver and transmitter of video data with two input channels (channel 0 and 1) and two output channels (channel 2 and 3). Channels 0 and 1 have the same architecture, and channels 2 and 3 have the same architecture. The register settings include EAV2SAV, SAV2EAV, L1, L3, L5 and VSIZE, as shown in the following figure:

L1 is the first line of upper blanking for the frame

L3 is the first line of the frame for active video area

L5 is the first line of lower blanking for the frame

vsize is the vertical size of the image

DM646x VPIF Settings

EAV2SAV is set based on the HBLANK (or equivalent) register setting in the video decoder. Usually

EAV2SAV = Horizontal Blanking Pixels - 8

sav2eav is the number of pixels per line

L3 is the first line of the frame for active video area

L5 is the first line of lower blanking for the frame

vsize is the vertical size of the image

1 comment:

I'm currently coding an advanced E-EDID 1.4 editor.

Thanks for all the info.

It will include detailed timing data based on the CVT and GTF formula's...

Post a Comment